#### 1. Description

TM1809 is a 9-channel LED driver control IC. Internal integrated with MCU digital interface, data flip-latch, LED high voltage driver and so on .Through the external MCU control, the chip can achieve separate luminance, and through cascade control can achieve outdoor large-screen color dot-matrix light-emitting control. TM1809 have excellent performance and high reliability.

#### 2. Feature

- Use high-voltage power CMOS process

- Output pin tolerance voltage is up to 24V

- Input voltage can support 6 ~24V via outside resistance connected to chip VDD pin

- Build-in stabilized voltage supply circuit

- Brightness adjustment circuit(256 level)

- Signal line for series cascade interface

- Oscillation mode: Built-in double RC oscillator and clock synchronization

- Built-in power-on reset circuit

- PWM control side can achieve 256 adjustment, scan frequency not less than 400hz / s

- When the refresh rate is 30 frames/s, the number of cascade is not less than 540 on low-speed mode. And it is not less than 1080 on high-speed mode

- Data transmission speed have two selected mode (400Kbps and 800Kbps)

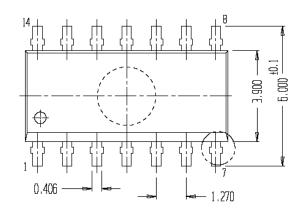

- SOP14

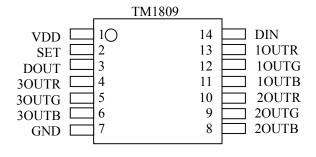

#### 3. PIN Configuration

## 4. PIN identifications

| PIN NO. | Configuration | PIN name             | Description                                                  |

|---------|---------------|----------------------|--------------------------------------------------------------|

| 14      | DIN           | Data in              | Display data in                                              |

| 3       | DOUT          | Data out             | Display cascade data out                                     |

| 2       | SET           | Set mode             | Connect to VDD: low-speed mode;<br>Floating: high-speed mode |

| 13      | 1OUTR         | LED driver output    | First red PWM control output                                 |

| 12      | 10UTG         | LED driver output    | First green PWM control output                               |

| 11      | 1OUTB         | LED driver output    | First blue PWM control output                                |

| 10      | 2OUTR         | LED driver output    | Second red PWM control output                                |

| 9       | 2OUTG         | LED driver output    | Second green PWM control output                              |

| 8       | 2OUTB         | LED driver output    | Second blue PWM control output                               |

| 4       | 3OUTR         | LED driver output    | Third red PWM control output                                 |

| 5       | 3OUTG         | LED driver output    | Third green PWM control output                               |

| 6       | 3OUTB         | LED driver output    | Third blue PWM control output                                |

| 1       | VDD           | Logical power supply | 5V±10%                                                       |

| 7       | GND           | Logical GND          | Connect to system GND                                        |

## 5. Electrical parameters

## Limited parameter ( $Ta = 25^{\circ}C$ , Vss = 0 V)

| Parameter                  | Symbol | Range      | Unit       |

|----------------------------|--------|------------|------------|

| Logic power supply voltage | VDD    | +4.5 ~+5.5 | V          |

| Output tolerance voltage   | VOUTx  | 24         | V          |

| Logic input voltage        | VI1    | V          |            |

| LED driver output current  | IO1    | 80         | mA         |

| Power Dissipation          | PD     | 400        | mW         |

| Operating Temperature      | Topt   | -40 ∼ +80  | $^{\circ}$ |

| Storage Temperature        | Tstg   | -65 ∼+150  | $^{\circ}$ |

## The normal scope of work (Ta = -20 $\sim$ +70°C, Vss = 0 V)

| Parameter                  | Symbol | Min     | Typical | Max.       | Unit | Test<br>Condition |

|----------------------------|--------|---------|---------|------------|------|-------------------|

| Logic power supply voltage | VDD    |         | 5       |            | V    | -                 |

| High-level voltage         | VIH    | 0.7 VDD | -       | VDD        | V    | -                 |

| Low-level voltage          | VIL    | 0       | -       | 0.3<br>VDD | V    | -                 |

# Electrical characteristics (Ta = -20 $\sim$ +70°C, VDD = 4.5 $\sim$ 5.5 V, Vss = 0 V

| Parameter                   | Symbol   | Min        | Typical | Max.       | Unit | Test Condition            |

|-----------------------------|----------|------------|---------|------------|------|---------------------------|

| Low-level output current    | IOL1     | 50         | 80      | -          | mA   | OUTR/OUTG/OUTB<br>Vo=0.3V |

| Low-level output current    | Idout    | 10         | -       | -          | mA   | VO = 0.4V, DOUT           |

| Input Current               | II       | -          | -       | ±1         | μΑ   | VI = VDD / VSS            |

| High-level input voltage    | VIH      | 0.7<br>VDD | -       |            | V    | DIN, SET                  |

| Low-level input voltage     | VIL      | -          | -       | 0.3<br>VDD | V    | DIN, SET                  |

| Hysteresis voltage          | VH       | -          | 0.35    | -          | V    | DIN, SET                  |

| Dynamic current consumption | IDDdyn   | -          | -       | 1          | mA   | No load, display off      |

| Power Dissipation           | PD       |            |         | 250        | mW   | (Ta=25°C)                 |

| Thermal Resistance          | Rth(j-a) | 79.2       |         | 190        | °C/W |                           |

## Switching characteristics (Ta = -20 $\sim$ +70°C, VDD = 4.5 $\sim$ 5.5 V)

| Parameter              | Symbol | Min | Typical | Max. | Unit | Test Condition                   |

|------------------------|--------|-----|---------|------|------|----------------------------------|

| Oscillation            | Fosc1  | i   | 400     | 1    | KHz  | /                                |

| frequency              | Fosc2  | 1   | 800     | 1    | KHz  | /                                |

|                        | tPLZ   | -   | -       | 300  | ns   | $\mathrm{DIN} \to \mathrm{DOUT}$ |

| Propagation delay time | tPZL   | -   | -       | 100  | ns   | $CL = 15pF, RL = 10K \Omega$     |

| Fall Time         | TTHZ | -   | - | 120 | μs   | CL = 300pF,<br>OUTR/OUTG/OUTB |

|-------------------|------|-----|---|-----|------|-------------------------------|

| Data rate         | Fmax | 400 | - | -   | Kbps | Duty rate 50%                 |

| Input capacitance | CI   | -   | - | 15  | pF   | -                             |

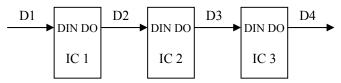

## **6. Function Description**

TM1809 adopts single wire to communicate and RZ (return to zero code) method to sent signal. On power-on reset status, when chip receive complete three groups of 24bits data from DIN, it begin transmitting data to next chip via DO. Before transmission, DO will be keep low-level. OUTR, OUTG, OUTB these 3 PWM will output different duty signal according to received data, the cycle of signal is 4ms.If input signal is RESET, the chip will be ready to receive new data after displaying all the received data. The same when receive new 3 groups of 24bit data completely, it will transmit them to next chip via DO.

TM1809 has the ability of auto-shape and signal transmission. The number of cascade is not limited by signal transmission, just limited by screen refresh speed. For example, we design 1080 cascade with 360ea TM1809 IC, the refresh time can be calculated is 360\*0.8\*2=0.576ms (delay time per IC is 0.8us), no any twinkle will be detected.

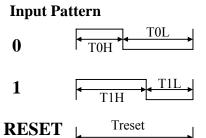

## 7. Timing Waveform

Low-speed mode time

| Name   | Description           | Min  | TYP  | Max  | Unit |

|--------|-----------------------|------|------|------|------|

| ТОН    | 0, high-level time    | 450  | 600  | 750  | ns   |

| T1H    | 1, high-level time    | 1050 | 1200 | 1350 | ns   |

| T0L    | 0, low-level time     | 1050 | 1200 | 1350 | ns   |

| T1L    | 1, low-level time     | 450  | 600  | 750  | ns   |

| Treset | Reset, low-level time | -    | 24   | >24  | us   |

**High-speed mode time**

| Name   | Description           | Min | TYP | Max | Unit |

|--------|-----------------------|-----|-----|-----|------|

| ТОН    | 0, high-level time    | 250 | 320 | 390 | ns   |

| T1H    | 1, high-level time    | 530 | 600 | 670 | ns   |

| T0L    | 0, low-level time     | 530 | 600 | 670 | ns   |

| T1L    | 1, low-level time     | 250 | 320 | 390 | ns   |

| Treset | Reset, low-level time | -   | 24  | >24 | us   |

## **Connection mode**

#### Data transmission method:

| D1 | RESET<br>CODE | Fisrt 72bit | Second 72bit | Third 72bit  | RESET | Another first72bit | Another | r Second  |

|----|---------------|-------------|--------------|--------------|-------|--------------------|---------|-----------|

|    |               |             |              |              | CODE  |                    | 72 bit  |           |

|    |               |             |              |              | RESET |                    |         | 0 1.70    |

|    |               |             | Second 72bit | Third 72bit  | CODE  |                    | 1       | Second 72 |

| D2 |               |             |              |              |       |                    | bit     |           |

| D2 |               |             |              | Third 72bit  | RESET |                    |         |           |

|    |               |             |              | 11111d /2010 | CODE  |                    |         |           |

| D3 |               |             |              |              |       |                    |         |           |

|    |               |             |              |              |       |                    |         |           |

| D4 |               |             |              |              |       |                    |         |           |

## 72bit data structure

| 1R7 | 1R6 | 1R5 | 1R4 | 1R3 | 1R2 | 1R1 | 1R0 | 1 <b>G</b> 7 | 1G6 | 1G5 | 1 <b>G</b> 4 | 1 <b>G</b> 3 | 1G2 | 1G1 | 1G0 |

|-----|-----|-----|-----|-----|-----|-----|-----|--------------|-----|-----|--------------|--------------|-----|-----|-----|

| 1B7 | 1B6 | 1B5 | 1B4 | 1B3 | 1B2 | 1B1 | 1B0 | 2R7          | 2R6 | 2R5 | 2R4          | 2R3          | 2R2 | 2R1 | 2R0 |

| 2G7 | 2G6 | 2G5 | 2G4 | 2G3 | 2G2 | 2G1 | 2G0 | 2B7          | 2B6 | 2B5 | 2B4          | 2B3          | 2B2 | 2B1 | 2B0 |

| 3R7 | 3R6 | 3R5 | 3R4 | 3R3 | 3R2 | 3R1 | 3R0 | 3G7          | 3G6 | 3G5 | 3G4          | 3G3          | 3G2 | 3G1 | 3G0 |

| 3B7 | 3B6 | 3B5 | 3B4 | 3B3 | 3B2 | 3B1 | 3B0 |              | •   |     | •            | •            | •   | •   | •   |

Upper bit first, sent data in accordance with R, G, B order.

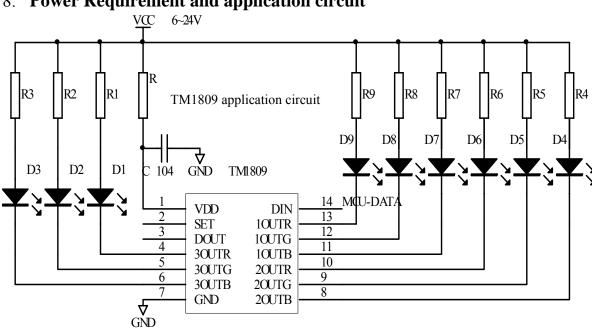

## 8. Power Requirement and application circuit

The capacitance 104 should near to IC power

According to different supply power voltage, different resistance is requested to add between power supply interface and VDD PIN of TM1809. The resistance as the below for application reference,

| Supply power | Resistance |

|--------------|------------|

| 6V           | 1K         |

| 9V           | 4K         |

| 12V          | 7K         |

| 24V          | 20K        |

VDD voltage keeps invariable 5v in the actual application. SET should be connected with VDD not with outside power VCC to prevent IC breakdown.

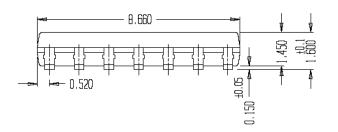

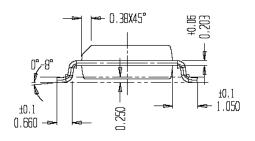

# 9. IC Package diagram SOP14: